- IBM Power

-

Dieser Artikel wurde aufgrund von inhaltlichen Mängeln auf der Qualitätssicherungsseite der Redaktion Informatik eingetragen. Dies geschieht, um die Qualität der Artikel aus dem Themengebiet Informatik auf ein akzeptables Niveau zu bringen. Hilf mit, die inhaltlichen Mängel dieses Artikels zu beseitigen und beteilige dich an der Diskussion! (+)

Begründung: Struktur, Entlisten --Crazy1880 10:01, 2. Jun. 2010 (CEST)Die IBM Power-Architektur (ein Backronym für Performance optimized with enhanced RISC) ist der Urvater und der Großrechnerzweig der PowerPC-CPU von IBM. Sie kommt (bis POWER4+) in den iSeries, ehemals AS/400, den pSeries, ehemals RS/6000, und inzwischen mit Power5+-Prozessoren in den Systemen IBM eServer p5 und eServer i5 zum Einsatz.

Aus der ursprünglichen Power-Familie wurde zunächst der Ein-Chip-Prozessor PowerPC 601 abgewandelt, später der PowerPC 970 aus dem Power4+. Dadurch konnte die Power-Architektur leichter in den Bereichen der Workstation-Computer, in eingebetteten Systemen sowie in der Raumfahrt verwendet werden.

Inhaltsverzeichnis

Power2

Aus dem 1993er Acht-Chip-Prozessor Power2 wurde 1996 der Power2 SC, der erste Power-Prozessor aus einem Chip, abgeleitet, und noch bis 1999 verkauft.

Power3

1998 erschienen der Power3 und der Power3-II mit 64-Bit-CMOS6S2-Technologie, und 225 mm² (Power3) bzw. 170 mm² (Power3-II) Die-Fläche.

Power4

Die IBM p690, genannt Regatta, realisierte erstmals auf einem Chip zwei CPU-Kerne (zunächst ab 2001 Power4, 180 nm, 1,1–1,3 GHz), einen gemeinsamen L2-Cache und eine sehr schnelle Switch-Schnittstelle. Aber auch die Verbindungsschnittstellen dieser Chips waren neuartig. So wurden vier dieser Prozessorkerne auf einem gemeinsamen Multi-Chip-Modul (MCM) verbunden; IBM erreichte damit die extrem hohe Packungsdichte von acht CPUs auf einer Fläche von 90 cm². Die Regatta erreichte mit 32 Power4+-CPUs (ab 2002: 130 nm, 1,2–1,9 GHz, 267 mm², 185 Mio. Transistoren) im März 2004 eine Spitzenleistung von über 1 Mio. Punkten im Datenbank-Benchmark tpm-C.

Power 5

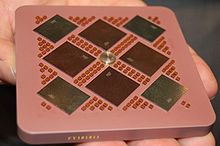

Power5-Vier-Core-MCM (2005)

Power5-Vier-Core-MCM (2005)

Power5 130 nm 1,5; 1,65; 1,9 GHz Dual-Core-Prozessor, 389 mm², 276 Mio. Transisitoren, mit Simultaneous Multithreading (SMT) und integriertem Speichercontroller. Cache: 64k2w-lru (Instruktionen) und 32k4w-lru (Daten). L2-Cache 1.92m10w-lru. in partitionierbaren pSeries und iSeries SMP-Servern von 1 bis 64 CPUs, 1 GB–2 TB Hauptspeicher und 5 – 240 PCI-X-Slots. Ein Multi-Chip-Module mit vier CPU-Chips (also acht Kernen) und vier 36 MB L3-Cache-Chips besteht aus 89 Metalllagen mit insgesamt 5370 I/O-Pins, von denen 2313 Signalpins sind und 3057 für die Energiezufuhr benötigt werden.

Power5 von 2004 ist die Weiterentwicklung von Power4. Zusätzlich zur Power4-Architektur befindet sich auf dem Chip das L3-Directory und der Memory-Controller, dazu kommt eine höhere Taktung. Power5 ist bis zu dreimal leistungsfähiger als Power4. IBM behauptete, dass dieses für die damals beste Skalierbarkeit (linear bis 64 Wege) aller am Markt angebotenen Server sorgte. Als weitere einzigartige Funktionalität bietet die Power5-Architektur mit der Advanced Power Virtualization (APV) unter anderem die Möglichkeit, die physikalischen CPUs in virtuelle CPUs aufzuteilen, die dann wieder zwischen den verschiedenen logischen Partitionen (LPARs) im laufenden Betrieb dynamisch und automatisch verteilt werden. APV wird seit dem 21. Dezember 2008 unter dem Namen PowerVM verkauft.

Am 4. Oktober 2005 kündigte IBM den Power5+ 90 nm Quad-Core an.

Power6

Der Power6-Prozessor wurde ab 2007 im 65-nm-Verfahren gefertigt und hat eine Die-Fläche von 341 mm². Auf dieser Fläche sind über 790 Millionen Transistoren[1]. Das meiste der Fläche wird vom 8 MiB fassenden L2-Cache belegt, wovon jedem Core die Hälfte, also 4 MiB, zugeteilt werden. Die Größe des L1-Caches ist 128 KiB, aufgeteilt in 64 KiB Daten- und 64 KiB Instruktionscache. Der externe L3-Cache in der Größe von 32 MiB ist mit einer Bandbreite von 80 GiB/s ansprechbar. Die Power6-Prozessoren sind mit 4,2; 4,7 und 5,0 GHz Taktfrequenz erhältlich.

IBM sieht diesen Prozessor im Bereich von Unternehmensdatenbanken (z.B. IBM System p und IBM System i) sowie Hochleistungsrechnern, wie sie im Flugzeugbau und bei Unfallsimulationen im Automobilbau benötigt werden.

Power7

Der Power7 ist 2010 auf den Markt gekommen und besteht aus bis zu acht Kernen, wovon jeder Kern parallel bis zu vier Threads ausführen kann. Die CPU wird in 45 nm gefertigt und die maximale Taktfrequenz liegt bei 4,1 GHz.[2][3]

Weblinks

- Timo Schöler: Nahaufnahme: IBM Power. (PDF, 404 KByte), Entwicklungen von IBMs Power-CPUs der letzten Jahre im Überblick, detaillierte Darstellung der in der Power5(+)-CPU genutzten Technologien (2005)

Einzelnachweise

Kategorie:- IBM-Prozessor

Wikimedia Foundation.